# FPGA Based Optimized Discontinuous SVPWM Algorithm for Three Phase VSI in AC Drives

By Tole Sutikno

Vol. 3, No. 2, June 2013, pp. 228~240

ISSN: 2088-8694

#### FPGA Based Optimized Discontinuous SVPWM Algorithm for Three Phase VSI in AC Drives

#### Tole Sutikno<sup>1</sup>, Nik Rumzi Nik Idris<sup>2</sup>, Auzani Jidin<sup>3</sup>, Mohd Hatta Jopri<sup>3</sup>

<sup>1</sup>Department of Electrical Engineering, Universitas Ahmad Dahlan, Yogyakarta (UAD), Indonesia <sup>2</sup>Department of Energy Conversion, Universiti Teknologi Malaysia (UTM), Johor, Malaysia <sup>3</sup>Department of Power Electronics and Drive, Universiti Teknikal Malaysia Melaka (UTeM), Malacca, Malaysia

#### Article Info

#### Article history:

Received Jan 25, 2013 Revised May 2, 2013 Accepted May 28, 2013

#### Keyword:

AC Drives Discontinuous SVPWM FPGA Switching losses Three Phase VSI

#### ABSTRACT

The discontinuous space vector pulse width modulation (SVPWM) has well-known that can reduce switching losses. By simplifying the thermal management issues, the discontinuous SVPWM can potentially reduce the inverter size and cost. However, using the modulation due to different time interval equations for each sector can introduce glitches at the points when the sector is changed. The more main problem, it can increase unwanted harmonic content and current ripple. Consider the decrease in switching losses associated with discontinuous modulation allows the system to utilize a higher switching frequency, this paper present high frequency switching of optimized discontinuous SVPWM based on FPGA to overcome the problems above. The proposed SVPWM has been successfully implemented by using APEX20KE Altera FPGA to drive on a three phase inverter system with 1.5 kW induction machine as load. The results have proved that the method can reduce the properties of the proposed successfully implemented by using the content and current ripple without glitches.

Copyright © 2013 Institute of Advanced Engineering and Science. All rights reserved.

#### Corresponding Author:

Tole Sutikno

Departement of Electrical Engineering,

Universi 22 Ahmad Dahlan,

Kampus 3 UAD, Jln. Prof. Dr. Soepomo, Janturan, Yogyakarta, Indonesia 55164

Email: tole@ee.uad.ac.id

#### 1. INTRODUCTION

The key requirements of any modulation method are to provide higher power output and efficiency for a wide range of inverter output voltage control. The SVPWM method is an advanced PWM method at which it is possibly the best among all the PWM techniques for variable frequency drive applications, since SVPWM can provide a better fundamental output voltage, better harmonic performance and easier be implemented [1-11].

The SVPWM strategies have been the focus of many years of research attempt. In recent years, the SVPWM method gradually obtains widespread applications in the power electronics and the electrical drives due to its superior performance characteristics. The SVPWM is more suitable for digital implementation compared to the SPWM, whereby the obtainable DC voltage utilization ratio can be highly increased. As the result, a better voltage THD factor can be obtained [1, 7, 9, 12-14].

The comparison of P<sub>L</sub>, T<sub>J</sub> junction IGBT, and weighted THD of the different modulation schemes are shown in Table 1 [15]. From the comparison, although the discontinuous SVPWM (or bus clamping SVPWM) gives a slightly higher of weighted THD compared with conventional SVPWM method, the result in lowest switching losses and lowest junction temperature of IGBT compared with the SPWM and conventional SVPWM. The switching loss of the discontinuous SVPWM is consistently lower than those of SPWM and SVPWM as there are fewer switching instants and that the dead-time effect is smaller since there is no switching during the DC clamped period.

Table 1. The comparison of the different modulation schemes [15]

| Parameters                        | SPWM | Conventional SVPWM | Discontinuous SVPWM |

|-----------------------------------|------|--------------------|---------------------|

| P <sub>L</sub> (per-unit of SPWM) | 1.00 | 1.33               | 0.83                |

| T <sub>J</sub> (increase, °C)     | 35   | 45                 | 32                  |

| Weighted THD (%)                  | 4.0  | 1.8                | 2.9                 |

At higher line-side voltages for a given average switching frequency, the discontinuous SVPWM have lower THD in line currents than the continuous SVPWM methods [2, 16-19]. The discontinuous SVPWM also provides a linear range of modulation index 0-115.4% [20]. It is, therefore, can increase the power handling capability of the converter, or its need for cooling, and increasing the converter power density. It is suitable to minimize the weight and volume of power electronics systems, as in electric vehicle and aircraft applications.

The discontinuous SVPWM initially developed by Depenbrock [21] in 1977. Currently, the discontinuous SVPWM has become one the most promising modern PWM methods which is used in various power electronics such as motor drives, front-end converter, and active filter. In general, it is now accepted that with discontinuous modulation having some advantages for higher modulation ratios [16, 22-28]. However, in the discontinuous SVPWM methods, the reduction in their switching loss does not exactly come free. There is a small drawback can introduce oscillations around the points where the sector is changed. This is due to the different set of equations used within each sector to calculate the time intervals. At low output fundamental frequencies, the effects will be clearer and they result in increased loss in the load and may cause instabilities of the feedback control system [5, 20, 29-31]. In this paper therefore the discontinuous SVPWM duty cycle is updated at specific times in the SVPWM period to avoid glitches in the PWM output signal.

The SVPWM algorithm is mainly implemented using software based on microcontroller or DSP [32-34]. Designers have to perform the control procedure sequentially by exploiting their mathematically oriented resources. That is the instructions of different procedures need to be executed one after the other. Thus, the purely software-based technique is not an ideal solution. The FPGA is an appropriate alternative over analog and software solutions (DSP and microcontroller) [35-39], and its architecture offers a significant integration density [40] within a flexible programmable environment. Designers can get a new degree of freedom by applying FPGA in SVPWM since their dedicated hardware architectures that match all the requirements in terms of control performance and implementation constraints can easily be realize [41].

Employing of FPGA in SVPWM methods offer a lot of advantages, such as: shorter design cycle, fair cost, rapid prototyping, simpler hardware and software design, and higher switching frequency. It is exactly different from software implementation, whereby the FPGA performs the entire procedures with concurrent operation (allow parallel processing by means of hardware mode and not occupying) by using its reconfigurable hardware. With the powerful computation ability and flexibility, an FPGA is quite mature for electrical drive application and it is considered as a solution to improve system performance of a digital controller, including a SVPWM algorithm [3, 41-47].

In many control applications, including SVPWM realization, the digital hardware FPGA-based solutions have been successfully used [3, 41, 43-46]. However, these conventional SVPWM suffers from the disadvantages like computational burden, low-grade performance at high modulation indices and high switching losses of the inverters. Therefore, several discontinuous SVPWM methods have been proposed to reduce the switching losses and to improve the performance in high modulation region [5, 13, 15, 16, 18-21, 26, 27, 48-55].

Although the researches of the implementation for three-phase SVPWM based on FPGA is not lacking, However, most of the designs are based on the conventional SVPWM without consideration of the hardware-resource saving and are more complex. In this paper, a new approach of FPGA-based SVPWM will discussed, where the judging of sectors and the calculation of the firing time to generate the SVPWM waveform is simple with low switching losses and hardware-resource saving. The quadrature voltages have be evaluated in time domain, as shown in Fig 1 to identify sector location. The proposed method is single stage comparator, so the identification will run quickly. As a result, the information of sector location will be informed only within one clock cycle to accurately select the voltage vectors. By using the relationship between carrier-based PWM and SVM, the calculating of the duration of active vectors will be represented in carrier based, so the calculation can be easily transformed in an equivalent space vector modulation modulator to generate SVM switching pulses. Therefore, it doesn't require for calculating the durations directly. The proposed SVPWM design will be implemented based on APEX20KE Altera FPGA.

#### 2. NOVEL METHOD OF SVPWM1LGORITHM

The SVPWM strategy aims to minimize harmonic distortion in the current by selecting the appropriate switching vectors and determining of their corresponding dwelling widths. The choice of the null

230

ISSN: 2088-8694

vector determines the SVPWM scheme. There are some options: the null vector V0 only, the null vector  $V_7$  only, or a combination of null vectors. The equivalent PWM waveforms, which produce the same average flux, may consist of varous combinations of the basic vectors. The characteristic of each those strategies above can be resumed as shown in Table 2.

Table 2. Comparison of SVPWM patterns

| No | Pattern SVPWM (based on sector                              | Number of | Number of commutation in | THD                | Easiness to implement |

|----|-------------------------------------------------------------|-----------|--------------------------|--------------------|-----------------------|

|    | 20 I)                                                       | segments  | one sampling period      |                    | in FPGA               |

| 1  | $20V_1-V_2-V_7-V_2-V_1-V_0$                                 | 7         | 6                        | low                | quiet-difficult       |

| 2  | $V_7 - V_2 - V_1 - V_0 - V_1 - V_2 - V_7$                   | 7         | 6                        | low                | quiet-difficult       |

| 3  | $V_1-V_2-V_7-V_2-V_1$                                       | 5         | 4                        | almost low         | easy                  |

| 4  | $V_0-V_1-V_2-V_1-V_0$                                       | 5         | 4                        | almost low         | easy                  |

| 5  | $V_0-V_1-V_2-V_7$                                           | 4         | 3                        | almost significant | not-easy              |

| 6  | $V_0-V_2-V_1-V_7$                                           | 4         | 3                        | almost significant | not-easy              |

| 7  | $V_1$ - $V_2$ - $V_7$ and $V_2$ - $V_1$ - $V_7$ alternately | 3         | 2 and 3 alternately      | higher significant | not-easy              |

The conventional principle of the SVPWM algorithm relies too much on the judging of sectors, firing time (duration of active vectors) calculation, and the method of switching sequence generating are too complex. As a solution to overcome the problems from the conventional SVPWM, the paper proposes the principle of a symmetrical five-segment discontinuous switching sequence that not yet been revealed yet as a novel method of SVPWM algorithm.

#### 2.1. Proposed SVPWM switching Pattern (five-segment discontinuous switching sequence)

It has been reported many discontinuous SVPWM patterns [3, 5, 52, 54, 56]. Unfortunately, these patterns performed with used a complicated algorithm and high switching losses that is not easily realized based on FPGA. This paper proposes a novel symmetric five-segment discontinuous SVPWM, the design of which mainly originated from the ideas of [33] and [57]. The pattern has been successfully DSP based implemented by Yu [33]. This pattern offered in lower switching losses, a simpler algorithm and easily implementation.

Therefore, in order to improve system performance, this paper will focus on implementation of discontinuous SVPWM pattern based on FPGA. There is always a leg that stays constant for the entire PWM period in this proposed pattern. The state sequence in this pattern is X-Y-Z-Y-X, where Z=1 in sector I, III and V, and Z=0 in the remaining sector. Thus, the number of switching time for this pattern is less than the conventional pattern, and the obvious result is reduced switching losses.

#### 2.2. Proposed identification of the sector

Several methods have been introduced to judge the sector where the reference space voltage vector lies. Zhi-pu [58] compared the reference space vector's angle with 00,  $60^{\circ}$ ,  $120^{\circ}$ ,  $180^{\circ}$ ,  $240^{\circ}$ , and  $300^{\circ}$  to achieve the number of the sector in which  $V_{ref}$  lies. Others, Yu [59], Jiang [60] and Xing [6] have analyzed the relationship between  $V_{\alpha}$  and  $V_{\beta}$  to determine the sector.

They have calculated the projections  $V_a$ ,  $V_b$  and  $V_c$  of  $V_\alpha$  and  $V_\beta$  in (a,b,c) plane by using the inverse Clark transformation, as follow:

$$\begin{cases} V_a = V_{\beta} \\ V_b = \frac{\sqrt{3}V_{\alpha} - V_{\beta}}{2} \\ V_c = \frac{-\sqrt{3}V_{\alpha} - V_{\beta}}{2} \end{cases}$$

(1)

Then, based on equation (1) and Table 3, N=sign(Va) + 2\*sign(Vb) + 4\*sign(Vc) and map N to the actual sector of the output voltage reference by referring to the following relationship N $\rightarrow$ sector: 1 $\rightarrow$ II, 2 $\rightarrow$ VI, 3 $\rightarrow$ I, 4 $\rightarrow$ IV, 5 $\rightarrow$ III, 6 $\rightarrow$ V. In [61], Zeliang et al. adopted two new intermediate vectors  $X_{\alpha}$  and  $X_{\beta}$  whereby  $X_{\alpha} = \frac{3}{2}V_{\alpha}$  and  $X_{\beta} = \sqrt{3}V_{\beta}$ .

| Sector | Vector Angle                 | $V_{\beta} > 0$ | $V_{\beta} > \sqrt{3}V_{\alpha}$ | $V_{\beta} > -\sqrt{3}V_{\alpha}$ |

|--------|------------------------------|-----------------|----------------------------------|-----------------------------------|

| I      | $(0^{\circ}, 60^{\circ})$    | 1               | 0                                | 1                                 |

| II     | $(60^{\circ}, 120^{\circ})$  | 1               | 1                                | 1                                 |

| III    | $(120^{\circ}, 180^{\circ})$ | 1               | 1                                | 0                                 |

| IV     | $(180^{\circ}, 240^{\circ})$ | 0               | 1                                | 0                                 |

| V      | $(240^{\circ}, 300^{\circ})$ | 0               | 0                                | 0                                 |

| VI     | $(300^{\circ}, 360^{\circ})$ | 0               | 0                                | 1                                 |

1: satisfy, 0: not satisfy

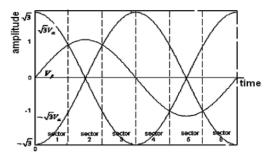

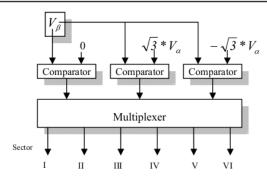

Decomposing the conventional SVPWM will properly counteract the redundant calculations to identify sector location, but it result in complicated matrix calculations. In this paper, by analyzing on the principle of SVPWM in [6, 59-61] and to reduce burden of computation, a new method to determine the sectors of voltage vectors based on comparison between  $V_{\beta}$ ,  $\sqrt{3}V_{\alpha}$ ,  $-\sqrt{3}V_{\alpha}$  and 0 as shown in Figure 1 is proposed. Through the comparison, sectors of voltage vectors as shown in Table 3 can be determined.

Figure 1. The plotting of  $V_{\beta}$ ,  $\sqrt{3}V_{\alpha}$ ,  $-\sqrt{3}V_{\alpha}$  wave

#### 2.3. The proposed calculation of the durational f active vectors

In this paper, a new set of equations to calculate the duration of active vectors for each sector has been re-arranged in order to construct an easier implementation based on FPGA. The space vector technique synthesizes a desired vector Vref from two adjacent actives,  $V_{\alpha}$  and  $V_{\beta}$  (among  $V_1$  and  $V_2$ , as shown in Fig.1) during time interval,  $T_a$  and  $T_b$ . The null vectors ( $V_0$  and  $V_7$ ) are also applied to reduce the inverter switching frequency. In the proposed design, only one null vector is inserted in a PWM period, whereby  $V_7$  for odd sector and  $V_0$  for even sector.

$$V_{\text{ref}} = V_{\alpha} + jV_{\beta} = \frac{2T_{\alpha}}{T} V_{\alpha} + \frac{2T_{b}}{T}$$

(2)

$$\frac{T}{2} = T_a + T_b + T_0 \tag{3}$$

Hence, the half PWM period T is composed of the switching time Ta, Tb and T0. The total time of the null vectors can be expressed as

$$T_0 = \frac{T}{2} - T_a - T_b \tag{4}$$

In this design, the switching time of the active vectors for each sector can be calculated as shown in Table 4.

Table 4. Switching time of the active vector for each sector

| Sector | 33                                                                                          | T                                                                                           | T +T                                                                                        |

|--------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| I      | $\frac{3T}{4} \left( \frac{V_{\alpha}}{V_{dc}} - \frac{V_{\beta}}{\sqrt{3}V_{dc}} \right)$  | $\frac{3T}{4} \frac{2V_{\beta}}{\sqrt{3}V_{dc}}$                                            | $\frac{3T}{4} \left( \frac{V_{\alpha}}{V_{dc}} + \frac{V_{\beta}}{\sqrt{3}V_{dc}} \right)$  |

| п      | $\frac{3T}{4} \left( \frac{V_{\alpha}}{V_{dc}} + \frac{V_{\beta}}{\sqrt{3}V_{dc}} \right)$  | $\frac{3T}{4} \left( -\frac{V_{\alpha}}{V_{dc}} + \frac{V_{\beta}}{\sqrt{3}V_{dc}} \right)$ | $\frac{3T}{4} \frac{2V_{\beta}}{\sqrt{3}V_{dc}}$                                            |

| Ш      | $\frac{3T}{4} \frac{2V_{\beta}}{\sqrt{3}V_{dc}}$                                            | $\frac{3T}{4} \Biggl( -\frac{V_\alpha}{V_{dc}} - \frac{V_\beta}{\sqrt{3}V_{dc}} \Biggr)$    | $\frac{3T}{4} \left( -\frac{V_{\alpha}}{V_{dc}} + \frac{V_{\beta}}{\sqrt{3}V_{dc}} \right)$ |

| IV     | $\frac{3T}{4} \left( -\frac{V_{\alpha}}{V_{dc}} + \frac{V_{\beta}}{\sqrt{3}V_{dc}} \right)$ | $-\frac{3T}{4}\frac{2V_{\beta}}{\sqrt{3}V_{dc}}$                                            | $\frac{3T}{4} \left( -\frac{V_{\alpha}}{V_{dc}} - \frac{V_{\beta}}{\sqrt{3}V_{dc}} \right)$ |

| v      | $\frac{3T}{4} \left( -\frac{V_{\alpha}}{V_{dc}} - \frac{V_{\beta}}{\sqrt{3}V_{dc}} \right)$ | $\frac{3T}{4} \left( \frac{V_{\alpha}}{V_{dc}} - \frac{V_{\beta}}{\sqrt{3} V_{dc}} \right)$ | $-\frac{3T}{4}\frac{2V_{\beta}}{\sqrt{3}V_{dc}}$                                            |

| VI     | $-\frac{3T}{4}\frac{2V_{\beta}}{\sqrt{3}V_{dc}}$                                            | $\frac{3T}{4} \left( \frac{V_{\alpha}}{V_{dc}} - \frac{V_{\beta}}{\sqrt{3}V_{dc}} \right)$  | $\frac{3T}{4} \left( \frac{V_{\alpha}}{V_{dc}} - \frac{V_{\beta}}{\sqrt{3}V_{dc}} \right)$  |

#### 2.4. Proposed method to generate SVPWM switching pulses

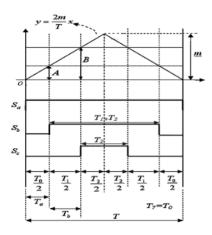

In this paper, a new method to generate SVPWM switching pulses is proposed, whereby by using comparison between the triangle waveform with  $T_a$  and  $T_a + T_b$ , the PWM signals for odd sectors are realized. High signal will be generate when the triangle waveform is higher than signal A or B, and another leg is always set to 1. While for the even sectors, the generation of PWM signal is complement with the odd sectors. Whereby signal will set high when the triangle waveform is lower than signal A or B and another one leg is set to 0.

To simplify the design process, the term  $\frac{2m}{T}$  will set to 1so that y will be always equal to x (x= $\frac{T_0}{2}$ ) =Ta then y=x=Ta, and if x= $\frac{T_1}{2}$ , then y= $\frac{T_1}{2}$ = $T_b$ ). Obviously if x= $\frac{T_0}{2}$ + $\frac{T_1}{2}$ = $T_a$ + $T_b$  then y= $\frac{T_0}{2}$ + $\frac{T_1}{2}$ = $T_a$ + $T_b$ . Therefore, the generation of PWM for S<sub>b</sub> and S<sub>c</sub> legs in sector I can be obtained by comparing the triangle waveform with  $T_a$ , and  $T_a$ + $T_b$  respectively and s<sub>a</sub> Leg is set to 1 due the odd sector position as shown in Figure 2.

Figure 2. Proposed SVPWM switching sequence generating method

#### 3. FPGA IMPLEMENTATION OF A PROPOSED NOVEL SVPWM

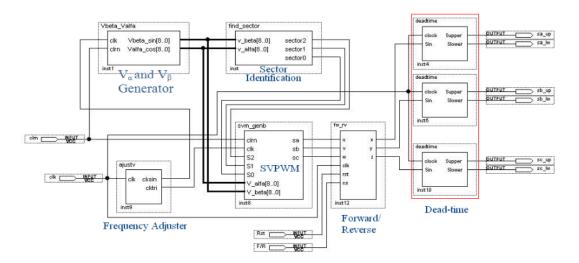

After the principle of SVPWM generation is discussed above, this section will focus on implementation of FPGA in SVPWM. To simplify the implementation based on FPGA, a graphical method has been devised to generate the SVPWM switching pulses. The overall proposed SVPWM design is shown in Figure 3. From this Fig, it consists of 6 blocks or modules, namely <code>ajust\_freq</code>, <code>Vbeta\_Valfa</code>, <code>find\_sector</code>, <code>SVPWM\_generator</code>, <code>fw-rv</code> and <code>deadtime\_sytem</code> modules. Each module is explained as follow:

Figure 3. The prototype of the proposed SVPWM design

#### 3.1. First Module: "ajust\_freq"

From Figure 3, the function of ajust\_freq is to generate a suitable clocking frequency. In the proposed SVPWM design, this module functions as a frequency divider by generating a carrier frequency of 20 kHz and a fundamental frequency of 50 Hz from the FPGA board, which have a clocking signal of 33.33Mhz. Since the triangle signal generator in this design is sampled to be 32 times per period, in order to get a carrier frequency of 20kHz, the main clock generator from FPGA board (pin L6)was divided by 13 (33.33MHz:(13 x32) =20kHz). The reference signal clocking is produced in a similar way.

#### 3.2. Second Module: "Vbeta\_Valfa"

In the proposed method,  $V_{alfa}$  and  $V_{beta}$  are generated based on sine and cosine functions through the look up table (LUT) with memory mapping. There have three lines which categories as lower, base and upper that represented to avoid overflow. With the memory mapping of 360 addresses, the counter mod-360 will used to count LUT of  $V_{alfa}$  and  $V_{beta}$ . In a similar way, the expansion of the module can be easily implemented. However, the using two's complement fixed-point format is more suggested compared to unsigned format as used in the prototype.

#### 3.3. Third Module: "find\_sector"

A reference voltage sector is necessary due to the different of switching time equations. The sector finder (SF) module in this design is used to judge the reference vector sector by referring to Table 3, is shown in Figure 4. This module determines the number of sectors and simplifies the truth table by comparing the above-mentioned results.

#### 3.4. Fourth Module: "SVPWM\_generator"

This module was divided into 4 sub modules, namely Triangle, Duration\_Ta, Duration\_TaTb, and SVPWM pattern module. Triangle module is functioned as triangle signal generator. The Duration\_Ta and Duration\_TaTb module are digital solutions for each second and fourth column, respectively. Finally, the SVPWM pattern module is used to generate the SVPWM sequence as described in section 2.4.

Figure 4. The proposed section determination

If it is assumed that T/VDC=1 and consider Figure 2 and Table 4, then the duration determination of Ta and Ta+Tb, and SVPWM pattern (switching status of Sa, Sb and Sc) can be calculated as shown in Table 5.

Table 5. The duration determination of  $T_a$  and  $T_a + T_b$ , and SVPWM pattern (switching status of  $S_a$ ,  $S_b$  and  $S_c$ )

|              |                        |                                      |                                             | -                                           |                       |

|--------------|------------------------|--------------------------------------|---------------------------------------------|---------------------------------------------|-----------------------|

| Sector       | Ta                     | $T_a+T_b$                            | Sa                                          | S <sub>b</sub>                              | S <sub>c</sub>        |

| I            | $V_d - 0.577V_q$       | $V_d + 0.577V_q$                     | 1                                           | Tri CP T <sub>a</sub>                       | Tri CP Ta+Tb          |

| II           | $V_d + 0.577 V_q$      | $+1.732V_{q}$                        | not (Tri) CP Ta                             | not (Tri) CP T <sub>a</sub> +T <sub>b</sub> | 0                     |

| Ш            | $1.155V_{q}$           | $-V_d$                               | Tri CP -(Ta+Tb)                             | 1                                           | Tri CP T <sub>a</sub> |

| IV           | $-V_d + 0.577V_q$      | $-V_d - 0.577V_q$                    | 0                                           | not (Tri) CP Ta                             | not (Tri) CP Ta+Tb    |

| $\mathbf{v}$ | $-V_d - 0.577V_q$      | - 1.732V <sub>q</sub>                | Tri CP Ta                                   | Tri CP Ta+Tb                                | 1                     |

| VI           | - 1.155 V <sub>a</sub> | V <sub>4</sub> - 0.577V <sub>a</sub> | not (Tri) CP T <sub>2</sub> +T <sub>5</sub> | 0                                           | not (Tri) CP T.       |

Tri: triangle signal; CP: compared to, "1" if equal or higher and "0" if lower; Not: NOT operation

#### 3.5. Fifth Module: "fw\_rv"

By including this module, we are possible to control forward and reverse motor direction. In this design, cs is used to change one of the forward or reverse control.

#### 3.6. Sixth Module: "deadtime\_system"

A dead-time of at least 2  $\mu$ s is required to avoid short circuit within a leg. Pair of 16-bits counter and 16 bits comparator is used to construct the dead time generator for each leg.

#### 4. RESULTS AND DISCUSSIONS

The software to design, perform compilation, verification and develop hardware based on the APEX20KE FPGA was developed under the Altera Quartus II, version 9.0. When compared with others methods, the proposed method required the minimum hardware resources. Tzou [3], Moreira [42], Zhaoyong [43], Guijie [47] and [56] consumed 2880, 1156, 3011, 1159, 3011 LEs respectively. The proposed SVPWM only consumed 520 LEs.

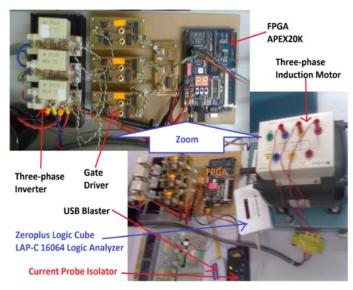

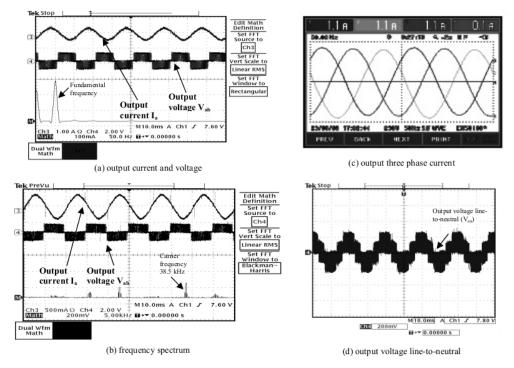

Fig 35 5 show output of the FPGA-based proposed disc 2 tinuous SVPWM generator which are acquired by Zeroplus Logic cube LAP-C 16064 logic analyzer. The photograph of the hardware experimental setup is shown on Figure 6.

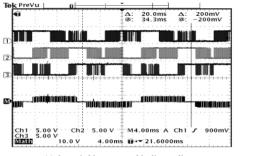

In this paper, the proposed SVPWM generator design with different carrier frequencies were successfully been carried out using of APEX20KE Altera FPGA. The results from hardware implementation with this proposed SVPWM generating method at carrier frequency of 20 kHz is shown in Figure 7. Probes 1, 2 and 3 in Figure 7 (a) and (b) represent switching state of  $S_a$ ,  $S_b$ , and  $S_c$ , respectively, whereby the probe M is a  $(S_a+S_b)$  line-to-line switching state with its frequency spectrum. From Figure 7 (b), the harmonics due to the 20 kHz switching frequency are clearly visible.

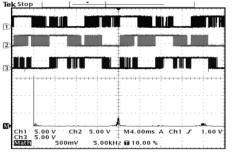

The similar condition is shown in Fig. 8. In this case, carrier frequency is set to 40 kHz, although the result in Fig. 8 (b) shows a 40 kHz. To test on the performance for the proposed SVPWM generator based

Figure 5. The comparison of required hardware resources

Figure 6. The hardware experimental setup

(a) the switching state and its line-to-line

(b) The signal gating and its frequency spectrum

Figure 7. Hardware implementation of proposed SVPWM generator at carrier frequency 20 kHz.

Figure 8. Hardware implementation of proposed SVPWM generator at carrier frequency 40 kHz.

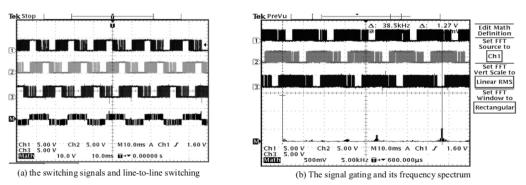

Figure 9. The performance of FPGA based proposed SVPWM generator design

The practical result for output stator current  $(I_a)$ , output phase-to-phase voltage  $(V_{ab})$ , frequency spectrum, output three phase current and output voltage line-to-neutral  $(V_{an})$  are shown in Fig. 9. The results shows that this proposed-SVPWM-generator based FPGA design is successful when implemented through a hardware platform. The practical results from the test-rig were as expected and showed that the proposed SVPWM generator design has successfully driven a 1.5 kW induction machine, with low current ripple. The result is in-line with [16] and [22] that the RMS current ripple at higher modulation indexes can be significantly reduced by using the discontinuous SVPWM.

Further, the comparison of current and voltage THD between the proposed SVPWM and other SVPWM is shown in Table 6. From the table, the proposed SVPWM shows a lower percentage in current and voltage THD compared with other SVPWM. However, the current THD from the proposed SVPWM (6.4%) is slightly higher than the hybrid type IV that proposed by Zhao *et al* [40] which is 6.34%. In addition, the

voltage THD is 11.10% and is slightly higher than the pattern III that proposed by Bharatiraja et al [56] with 9.90%.

Table 6. Comparison of current and voltage THD between the proposed SVPWM and other SVPWM

| Strategy                                                       | Current THD  | Voltage THD (%) | Fundamental    |

|----------------------------------------------------------------|--------------|-----------------|----------------|

|                                                                | (%)          |                 | frequency (Hz) |

| Proposed SVPWM based on FPGA                                   | 6.40         | 11.10           | 50             |

| Zhang and Yu [52]                                              |              |                 |                |

| <ul> <li>3-segment SVPWM</li> </ul>                            | not reported | 69.38           | 50             |

| <ul> <li>five-segment SVPWM</li> </ul>                         | not reported | 68.52           | 50             |

| <ul> <li>7-segment SVPWM</li> </ul>                            | not reported | 66.59           | 50             |

| Narayanan et al [53]                                           |              |                 |                |

| <ul> <li>Conventional SVPWM</li> </ul>                         | 20.29        | not reported    | 60             |

| <ul> <li>Discontinuous SVPWM</li> </ul>                        | 15.37        | not reported    | 60             |

| <ul> <li>Three-zone hybrid PWM</li> </ul>                      | 13.00        | not reported    | 60             |

| <ul> <li>Five-zone hybrid PWM</li> </ul>                       | 12.72        | not reported    | 60             |

| <ul> <li>Seven-zone hybrid PWM</li> </ul>                      | 12.58        | not reported    | 60             |

| Bharatiraja et al [56]                                         |              |                 |                |

| - pattern I                                                    | 15.07        | 17.60           | 50             |

| - pattern II                                                   | 19.31        | 9.90            | 50             |

| - pattern III                                                  | 23.96        | 24.27           | 50             |

| Saad et al [62]                                                |              |                 |                |

| - Rising-edge aligned sequence scheme                          | not reported | 54.49           | not reported   |

| (SVPWM1)                                                       | not reported | 54.47           | not reported   |

| <ul> <li>Falling-edge aligned sequence scheme</li> </ul>       | not reported | 54.45           | not reported   |

| (SVPWM2)                                                       | not reported | 39.86           | not reported   |

| <ul> <li>Symmetric aligned sequence scheme (SVPWM3)</li> </ul> |              |                 |                |

| <ul> <li>Alternative sequence scheme (SVPWM4)</li> </ul>       |              |                 |                |

| Zhao et al [63]                                                |              |                 |                |

| <ul> <li>Conventional SVPWM</li> </ul>                         | 10.07        | not reported    | 50             |

| <ul> <li>Minimum switching loss PWM (MSLPWM)</li> </ul>        | 10.11        | not reported    | 50             |

| <ul> <li>Discontinuous SVPWM</li> </ul>                        | 7.64         | not reported    | 50             |

| - Hybrid Type I                                                | 6.43         | not reported    | 50             |

| - Hybrid Type IV                                               | 6.34         | not reported    | 50             |

#### 5. CONCLUSION

This paper has proposed an advanced discontinuous (bus clamping) space vector modulation which employ special switching sequences and its implement special technique in FPGA hardware to get higher performance in term both in line current distortion as well as inverter switching losses, and also both in term of the hardware resources saving and the ease of implementing. The patter symmetrical will not degrade the control performance. The center-pulse switching pattern results will allow reducing the commutation losses and/or the harmonic content of output voltage, and to obtain higher amplitude modulation indexes if compared with conventional SVM. We have transformed the calculating of the duration of active vectors into an equivalent space vector modulation modulator to generate SVM switching pulses such as carrier-based PWM, so the calculation can be easily and fastly implemented in FPGA. The proposed SVPWM scheme has been successfully designed and implemented through the APEX20KE Altera FPGA in valuable hardware resources saving, without computing the number and angles of each sector as well as the commutation pattern. The practical results from the test-rig with a carrier frequency up to 40 kHz were as expected and showed that the proposed SVPWM generator design has successfully driven a 1.5 kW induction machine, with low current ripple and lower percentage in current and voltage THD compared with other SVPWM.

#### ACKNOWLEDGEMENTS

The authors would like to thank the Ministry of Higher Education of the Malaysian government, UTM and UTeM for providing the funding for this research.

#### REFERENCES

- van der Broeck HW, Skudelny HC, Stanke GV. Analysis and realization of a pulsewidth modulator based on voltage space vectors. IEEE Transactions on Industry Applications. 1988;24:142-50.

- [2] Holtz 5 Pulsewidth modulation-a survey. IEEE Transactions on Industrial Electronics. 1992;39:410-20.

- [3] Tzou Y-Y, Hsu H-J. FPGA realization of space-vector PWM control IC for three-phase PWM inverters. IEEE 13 nsactions on Power Electronics. 1997;12:953-63.

- [4] Bong-Hwan K, Tae-Woo K, Jang-Hyoun Y. A novel SVM-based hysteresis current controller. IEEE Transactions on Power Electronics. 1998;13:297-307.

Keliang Z, Danwei W. Relationship between space-vector modulation and three-phase carrier-based PWM: a comprehensive analysis. IEEE Transactions on Industrial Elec 29 ics. 2002;49:186-96.

- [6] Xing S, Zhao K-Y. Research on A Novel SVPWM Algorithm. Industrial Electronics and Applications, 2007 ICIEA 2007 2nd IEEE Conference on 2007. p. 1869-72.

- [7] Naguib MF, Lopes L. Minimize Low-Order Harmonics in Low-Switching-Frequency Space-Vector-Modulated Current Source Converters With Minimum Harmonic Tracking Technique. IEEE Transactions on Power Electronics. 2009;24:881-93.

- [8] Yinhai Z, Songsong W, Haixia X, Jinfa G. A Novel SVPWM Modulation Scheme. Applied Power Electronics Conference and Exposition, 2009 APEC 2009 Twenty-Fourth Annual IEEE2009. p. 128-31.

- [9] Lopes L, Naguib MF. Space Vector Modulation for Low Switching Frequency Current Source Converters With Reduced Low-Order Noncharacteristic Harmonics. IEEE Transactions on Power Electronics. 2009;24:903-10.

- [10] Sutikno T, Jidin A, Basar MF. Simple Realization of 5-Segment Discontinuous SVPWM Based on FPGA. International Journal of Computer and Electrical Engineering. 2010;2:148-57.

- [11] Sutikno T, Hwa WJ, Jidin A, Idris NRN. A simple approach of space-vector pulse width modulation realization based on field programmable gate array. Elect Power Components and Systems. 2010;38:1546-11.

- [12] Casadei D, Serra G, Tani K. Implementation of a direct control algorithm for induction motors based on discrete space vector modulation. IEEE Transactions on Power Electronics. 2000;15:769-77.

- [13] Holmes DG, McGrath BP. Opportunities for harmonic cancellation with carrier-based PWM for two-level and 21 tilevel cascaded inverters. IEEE Transactions on Industry Applications. 2001;37:574-82.

- [14] Bose BK. Modern Power Electronics and AC Drives. New Jersey: Prentice-Hall PTR; 2002.

- [15] Mehrizi-Sani A, Filizadeh S, Wilson PL. Harmonic and Loss Analysis of Space-Vector Modulated Converters. 18 rnational Conference on Power Systems Transients (IPST'07). Lyon, FranceJune 4-7, 2007.

- [16] Holmes D, Lipo T. Pulse Width Modulation for Power Converters: Principles and Practice: Wiley-IEEE Press 2003.

- [17] Kolar JW, Ertl H, Zach FC. Minimizing the current harmonics RMS value of three-phase PWN 8 poverter systems by optimal and suboptimal transition between continuous and discontinuous modulation. Power Electronics Specialists Conference, 1991 PESC '91 Record, 22nd Annual IEEE1991. p. 372-81.

- [18] Bhavsar T, Narayanan G. Harmonic Analysis of Advanced Bus-Clamping PWM Techniques. IEEE Transactions on Power Electronics. 2009;24:2347-52.

- [19] Narayanan G, Krishnamurthy HK, Zhao D, Ayyanar R. Advanced bus-clamping PWM techniques based on space vector approach. IEEE Transactions on Power Electronics. 2006;21:974-84.

- [20] Wu YX, Shafi MA, Knight AM, McMahon RA. Comparison 11 the Effects of Continuous and Discontinuous PWM Schemes on Power Losses of Voltage-Sourced Inverters for Induction Motor Drives. IEEE Transactions on Power Electronics. 201 7 6:182-91.

- [21] Depenbrock M. Pulse width control of a 3-phase inverter with nonsinusoidal phase voltages. IEEE-IAS Int Semiconductor Power Converter Conference1977. p. 399 -403.

- [22] Casadei D, Serra G, Tani A, Zarri L. Theoretical and experimental analysis for the RMS current ripple minimization in induction motor drives controlled by SVM technique. *IEEE Transactions on Industrial* 4ectronics. 2004;51:1056-65.

- [23] Dalessandro L, Round SD, Drofenik U, Kolar JW. Discontinuous space-vector modulation for three-level PWM rectifiers. IEEE Transactions on Power Electronics. 2008;23:530-42.

- [24] Asiminoaei L, Rodriguez P, Blaabjerg F, Malinowski M. Reduction of Switching Losses in Active Power Filters With a New Generalized Discontinuous-PWM Strategy. IEEE Transactions on Industrial Electronics. 2008;55:467-71.

- [25] Asiminoaei L, Rodriguez P, Blaabjerg F. Application of Discontinuous PWM Modulation in Active Power Filters. 16 E Transactions on Power Electronics. 2008;23:1692-706.

- [26] Basu K, Prasad JSS, Narayanan G. Minimization of Torque Ripple in PWM AC Drives. IEEE Transactions on Industrial Electronics. 2009;56:553-8.

- [27] Hava AM, x, etin NO. A Generalized Scalar PWM Approach With Easy Implementation Features for Three-Phase, Three-Wire Voltage-Source Inverters. IEEE Transactions on Power Electronics. 2011;26:1385-95.

- [28] Prieto J, Jones M, Barrero F, Levi E, Toral S. Comparative Analysis of Discontinuous and Continuous PWM Techniques in VSI-Fed Five-Phase India on Motor. *IEEE Transactions on Industrial Electronics*. 2011;PP:1-.

- [29] Zhang XF, Yu F, Li HS, Song QG. A novel discontinuous space vector PWM control for multiphase inverter. Power Electronics, Electrical Drives, Automation and Motion, 2006 SPEEDAM 2006 International Symposium on 2006. p. 1133-6.

- [30] Sutikno T, Jidin A, Idris NRN. New approach FPGA-based implementation of discontinuous SVPWM. Turkish Journal of Electrical Engineering and Computer Sciences. 2010;18:499-514.

- [31] Prieto J, Jones M, Barrero F, Levi E, Toral S. Comparative Analysis of Discontinuous and Continuous PWM Techniques in VSI-Fed Five-Phase Induction Motor. IEEE Transactions on Industrial Electronics. 2011;58:5324-

- [32] Gui-jie Y, Li S, Nai-zheng C, Yong-ping L. Study on Method of the space vector PWM. CSEE. China 2001. p. 79-83.

- [33] Yu Z. Space-Vector PWM With TMS320C24x/F24x Using Hardware and Software Determined Swithing Patterns. Digital Signal Processing Solutions: Texas Instruments; 1999. p. 1-24.

- [34] Fyntanakis A, Adamidis G, Koutsogiannis Z. Comparison between tw 28 ifferent methods of calculation of switching time which is used for implementation of SVPWM using DSP. Electrical Machines, 2008 ICEM 2008 144 International Conference on 2008, p. 1-6.

- [35] Monmasson E, Chapuis YA. Contributions of FPGA's to the Control of Electrical Systems: A Review. IEEE Ind Electron Soc Newsletter. 2002;49 no.4:8-15.

- [36] Rodriguez-Andina JJ, Moure MJ, Valdes MD. Features, Design Tools, and Application Domains of FPGAs. IEEE Transactions on Industrial Electronics. 2007;54:1810-23.

- [37] Monmasson E, Cirstea MN. FPGA Design Methodology for Industrial Control Systems: A Review. IEEE Transactions of Industrial Electronics. 2007;54:1824-42.

- [38] Xuefang L-S, Morel F, Llor AM, Allard B, Retif JM. Implementation of Hybrid Control for Motor Drives. IEEE Transactions on Industrial Electronics. 2007;54:1946-52.

- [39] Acero J, Navarro D, Barraga LA, Garde I, Artigas JI, Burdio JM. FPGA-Based Power Measuring for Induction Heating Appliances Using Sigma Delta A/D Conversion. IEEE Transactions on Industrial Electronics. 2007;54:1843-52.

- [40] Idkhajine L, Monmasson E, Naouar W, Prata A, Bouallaga K. Fully integrated FPGA-based controller for synchronous motor drive. IEEE Transactions on Industrial Electronics. 2009;56:4006 - 17.

- [41] Naouar MW, Monmasson E, Naassani AA, Slama-Belkhodja I, Patin N. FPGA-Based Current Controllers for AC Machine Drives-A Review. IEEE Transactions on Industrial Electronics, 2007;54:1923.25.

- [42] Moreira CS, Freire RCS, Melcher EUK, Deep GS, Catunda SYC, Alves RNC. FPGA-based SVPWM trigger generator for a 3-phase voltage source inverter. Instrumentation and Measurement Technology Conference, 2000 IMTC 2000 Proceedings of the 17th IEEE2000. p. 174-8 vol.1.

- [43] Zhaoyong Z, Tiecai L, Takahashi T, Ho E. Design of a universal space vector PWM controller based on FPGA. Applied Power Electronics Conference and Exposition, 2004 APEC '04 Nineteenth Annual IEEE2004. p. 1698-702 Vol.3.

- [44] Zhou Y, Xu F-p, Zhou Z-y. Realization of an FPGA-Based Space-Vector PWM Controller. Power Electronics and Motion Control Conference, 2006 IPEMC 2006 CES/IEEE 5th International 2006. p. 1-5.

- [45] Queiroz KIPM, Sousa FRd, Ribeiro RLA, Braz EC. A Flexible SVPWM implemented in FPGA. ftp://kuriosiuri:web@usersdcaufmbr/artigos/fsvpwm\_cobep\_2007pdf. 2007.

- [46] Ning-Yi D, Man-Chung W, Fan N, Ying-Duo H. A FPGA-Based Generalized Pulse Width Modulator for Three-Leg Center-Split and Four-Leg Voltage Source Inverters. IEEE Transactions on Power Electronics. 2008;23:1472-84.

- [47] Guijie Y, Pinzhi Z, Zhaoyong Z. The Design of SVPWM IP Core Based on FPGA. Embedded Software and Systems Symposia, 2008 ICESS Symposia '08 International Conference on 2008. p. 191-6.

- [48] Trzynadlowski AM. Nonsinusoidal modulating functions for three-phase inverters. Power Electronics, IEEE Transactions on. 1989;4:331-8.

- [49] Trzynadlowski AM, Legowski S. Minimum-loss vector PWM strategy for three-phase inverters. IEEE Transactions on Power Electronics. 1994;9:26-10

- [50] Trzynadlowski AM, Kirlin RL, Legowski SF. Space vector PWM technique with minimum switching losses and a variable pulse rate. IEEE Transactions on Industrial Electronics. 1997;44:173-81.

- [51] Trzynadlowski AM, Borisov K, Li Y, Qin L. A novel random PWM technique with low computational overhead and constant sampling frequency for high-volume, low-cost applications. *IEEE Transactions on Power Electronics*. 275;20:116-22.

- [52] Zhang W-F, Yu Y-H. Comparison of Three SVPWM Strategis. Journal of Electronic Science and Technology of China. 2007;5 no.3:283-7.

- [53] Narayanan G, Zhao D, Krishnamurthy HK, Ayyanar R, Ranganathan VT. Space Vector Based Hybrid PWM Techniques for Reduced Current Ripple. IEEE Transaction on Industrial Electronics. 55, No. 4, April 2008:1614-27.

- [54] Gowri KS, Redd TB, Babu CS. Novel Space Vector Based Generalized Discontinuous PWM Algorithm for Induction Motor Drives. ARPN Journal of Engineering and Applied Sciences. 2009;4 no.1.

- [55] Zhao D, Hari VSSPK, Narayanan G, Ayyanar R. Space-Vector-Based Hybrid Pulsewidth Modulation Techniques for Reduced Harmonic Distortion at 19 witching Loss. *IEEE Transactions on Power Electronics*. 2010;25:760-74.

- [56] Bharatiraja C, Prasad TB, Latha R. Comparative Realization of Different SVPWM Schemes in Linear Modulation Using FPGA. IEEE Region 8 S 15 on 2008. p. 164-8.

- [57] Trzynadlowski AM, Kirlin RL, Legowski S. Space vector PWM technique with variable pulse rate. Industrial Electronics, Control, and Instrumentation, 1993 Proceedings of the IECON '93, International Conference on 1993. p. 689-94 vol.2.

- [58] Zhi-pu Z. Design and Realization of Space Vector PWM Based on SG. *Drive and Control*. 2005;7:29-32.

- [59] Yu F, Yan X, Yuwen H. A fast algorithm for SVPWM in three phase power factor correction application. Electronics Specialists Conference, 2004 PESC 04 2004 IEEE 35th Annual2004. p. 976-9 Vol.2.

- [60] Jiang S, Liang J, Liu Y, Yamazaki K, Fujishima M. Modeling and cosimulation of FPGA-based SVPWM control for PMSM. Industrial Electronics Society, 2005 IECON 2005 31st Annual Conference of IEEE2005. p. 6 pp.

- [60] Zeliang S, Jian T, Yuhua G, Jisan L. An Efficient SVPWM Algorithm With Low Computational Overhead for Three-Phas 17 verters. IEEE Transactions on Power Electronics. 2007;22:1797-805.

- [62] Saad NH 34 Meged A, Mahmoud A. Comparison of state space vector PWM schemes for a voltage source inverter. Computer Engineering & Systems, 2008 ICCES 2008 International Conference on 2008. p. 303-8.

| ISSN: 2088-869                                                                                                   |                                                                                           | 240 🗆           |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------|

| ector Based Hybrid Pulse Width Modulation Techniques for<br>E Transactions on Power Electronics. 2010;25:760-74. | Chao D, Hari VPK, Narayanan G, Ayyanar R. S, Reduced Harmonic Distortion and Switching Lo | [63] Zhao Reduc |

|                                                                                                                  |                                                                                           |                 |

|                                                                                                                  |                                                                                           |                 |

|                                                                                                                  |                                                                                           |                 |

|                                                                                                                  |                                                                                           |                 |

|                                                                                                                  |                                                                                           |                 |

|                                                                                                                  |                                                                                           |                 |

|                                                                                                                  |                                                                                           |                 |

|                                                                                                                  |                                                                                           |                 |

|                                                                                                                  |                                                                                           |                 |

|                                                                                                                  |                                                                                           |                 |

|                                                                                                                  |                                                                                           |                 |

|                                                                                                                  |                                                                                           |                 |

|                                                                                                                  |                                                                                           |                 |

|                                                                                                                  |                                                                                           |                 |

## FPGA Based Optimized Discontinuous SVPWM Algorithm for Three Phase VSI in AC Drives

**ORIGINALITY REPORT**

9%

SIMILARITY INDEX

#### **PRIMARY SOURCES**

- Abdelli, R.. "Performances improvements and torque ripple minimization for VSI fed induction machine with direct control torque", ISA Transactions, 201104  $^{\text{Crossref}}$

- 2 tel.archives-ouvertes.fr  $_{\text{Internet}}$  29 words -<1%

- www.ijert.org

- Tao Wang, Changsong Chen, Peng Liu, Tianchang 21 words < 1 % Liu, Zeyun Chao, Shanxu Duan. "A Hybrid Space-Vector Modulation Method for Harmonics and Current Ripple Reduction of Interleaved Vienna Rectifier", IEEE Transactions on Industrial Electronics, 2019

- Morel, F.. "A predictive current control applied to a permanent magnet synchronous machine, comparison with a classical direct torque control", Electric Power Systems Research, 200808

Crossref

- Prima Dewi Purnamasari, Evan G. Sumbayak, Vicky Dwi Kurniawan, RR. Wulan Apriliyanti. "CO Pollution Warning System for Indoor Parking Area Using FPGA",

### International Journal of Reconfigurable and Embedded Systems (IIRES), 2013

Crossref

| 7 | V. Kaura, V. Blasko. "Operation of a voltage source converter at increased utility voltage", IEEE Transactions on Power Electronics, 1997 Crossref | 19 words — < 1 % |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 8 | mafiadoc.com<br>Internet                                                                                                                           | 19 words — < 1 % |

19 words

$$-<1\%$$

| 9 | the state of the s | 19 words — < 1 %         |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 9 | Internet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19 words — <b>&lt; Ⅰ</b> |

- 18 words < 1%"Design of subordinate control system with two 10 degrees of freedom", Power Engineering Control and Information Technologies in Geotechnical Systems, 2015. Crossref

- $_{18 \text{ words}} = < 1\%$ M KAZMIERKOWSKI. "Pulse Width Modulation Techniques for Three-Phase Voltage Source Converters", Control in Power Electronics, 2003 Crossref

- 18 words -<1%Sandor Halasz, Zalan Kohari. "Torque pulsations 12 of multiphase inverter-fed ac motors", Proceedings of 14th International Power Electronics and Motion Control Conference EPE-PEMC 2010, 2010 Crossref

- users.utcluj.ro

Internet

17 words < 1 %

- Taha Lahlou, Shah Nawaz Malik, Hans-Georg Herzog. "Simulation and analysis of control and modulation schemes for a multilevel cascaded H-bridge inverter for use in a battery energy storage system", 2017 18th International Scientific Conference on Electric Power Engineering (EPE), 2017

Crossref

- www.mdpi.com

Internet

16 words < 1 %

- www.srmuniv.ac.in 14 words < 1%

- Patin, Nicolas, and Vincent Lanfranchi. "Space Vector Modulation Strategies", Power Electronic Converters PWM Strategies and Current Control Techniques, 2013.

Crossref

- journals.sagepub.com 13 words < 1%

- sintadev.ristekdikti.go.id

13 words < 1%

Crossref

projekter.aau.dk

- 12 words < 1%

- Antonio Cataliotti, Fabio Genduso, Angelo Raciti, Giuseppe Ricco Galluzzo. "Generalized PWM–VSI Control Algorithm Based on a Universal Duty-Cycle Expression: Theoretical Analysis, Simulation Results, and Experimental Validations", IEEE Transactions on Industrial Electronics, 2007

Crossref

26 xplorestaging.ieee.org

- 11 words -<1%

- Li, Xiangfeng, Dongyuan Qiu, and Bo Zhang.

"Three-mode pulse-width modulation of a three-phase four-wire inverter", IET Power Electronics, 2015.

Crossref

- P. Karutz. "Magnetically levitated slice motors an overview", 2009 IEEE Energy Conversion Congress and Exposition, 09/2009

Crossref

- 10 words -<1%

gs1.dlut.edu.cn

10 words -<1%

30 tud.qucosa.de

10 words -<1%

$$_{10 \text{ words}} = < 1\%$$

Feri Yusivar, Nanda Avianto Wicaksono, Aries Subiantoro, Ridwan Gunawan. "Control of DFIG Stator Voltage on Autonomous Micro Hydro Power Plant", International Journal of Power Electronics and Drive Systems (IJPEDS), 2016

Crossref

Guido Herrmann. "Discretization Of A Non-Linear, Continuous-Time Control Law With Small Control Delays", Asian Journal of Control, 10/22/2008

8 words — < 1%

pdfs.semanticscholar.org

8 words = < 1%

www.nkcelectronics.com

- 8 words = < 1%

- Jesus Sallan. "Development of a new connection scheme for variable-speed wind turbines using squirrel-cage generators", IECON 2006 32nd Annual Conference on IEEE Industrial Electronics, 11/2006

- 7 words < 1%

Ruuhwan Ruuhwan, Imam Riadi, Yudi Prayudi.  $_{7 \text{ words}} - < 1\%$  "Evaluation of Integrated Digital Forensics Investigation Framework for the Investigation of Smartphones Using Soft System Methodology", International Journal of Electrical and Computer Engineering (IJECE), 2017

EXCLUDE QUOTES OFF

EXCLUDE BIBLIOGRAPHY OFF

EXCLUDE MATCHES OFF